8781

## QuASH

### (Quad Addressable Sample & Hold)

# ASSEMBLY INSTRUCTIONS

#### SOLDERING

Use care when mounting all components. Use only rosin core solder (acid core solder is never used in electronics work). A proper solder joint has just enough solder to cover the round soldering pad and about 1/16—inch of the lead passing through it. There are two improper connections to beware of: Using too little solder will sometimes result in a connection which appears to be soldered but actually there is a layer of flux insulating the component lead from the solder bead. This situation can be cured by reheating the joint and applying more solder. If too much solder is used on a joint there is the danger that a conducting bridge of excess solder will flow between adjacent circuit board conductors forming a short circuit. Unintentional bridges can be cleaned off by holding the board upside down and flowing the excess solder off onto a clean, hot soldering iron.

Select a soldering iron with a small tip and power rating of not more than 35 watts. Soldering guns are completely unacceptable for assembling transistorized equipment because the large magnetic field they generate can damage solid state components.

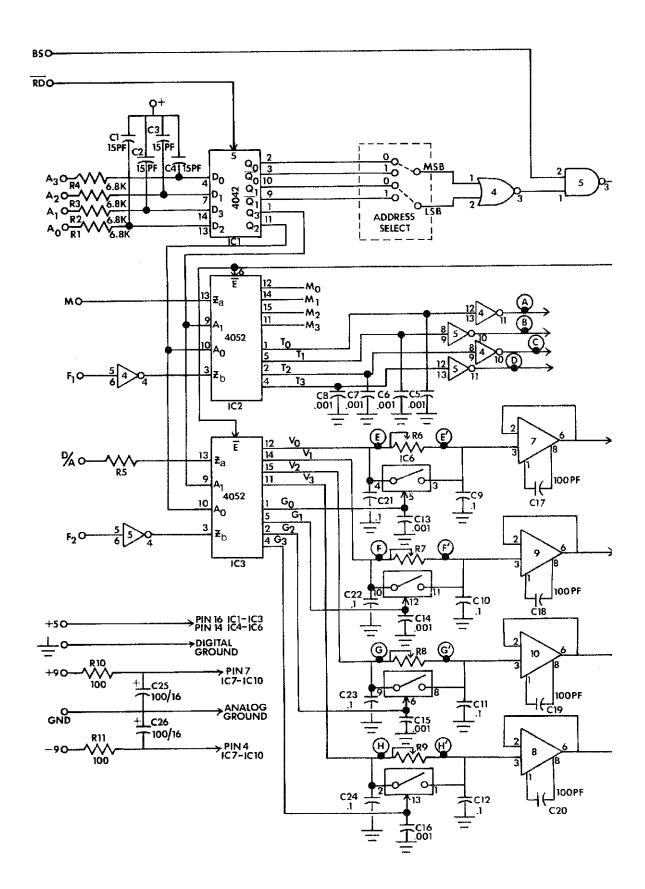

#### CIRCUIT BOARD ASSEMBLY

- (/) Prepare the circuit board for assembly by thoroughly cleaning the conductor side with a scouring cleanser. Rinse the board with clear water and dry completely.

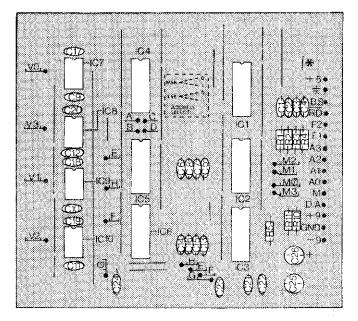

- Using the bare wire provided, form and install 27 jumpers as indicated by the solid lines in figure 1 and printed on the circuit board. When finished, count the jumpers to verify that 27 have been installed. Note that this number does not include the jumpers which will be installed within the dashed box labeled "address select". These jumpers will be installed later.

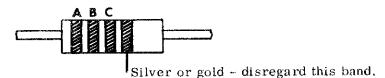

Solder each of the fixed resistors in place following the parts placement designators printed on the circuit board and the assembly drawing figure 1. Note that the fixed resistors are non-polarized and may be mounted with either of their two leads in either of the holes provided. Cinch the resistors in place prior to soldering by putting their leads through the holes and pushing them firmly against the board. On the conductor side of the board bend the leads outward to about a 45° angle. Clip off each lead flush with the solder joint as the joint is made.

| DESI         | GNATION             |   | VALUE     |   |   |   |   |   | ( | C | LOR CODE A-B-C    |

|--------------|---------------------|---|-----------|---|---|---|---|---|---|---|-------------------|

| (4)          | R1-R4 (4 parts)     |   | 6800 ohms | • | • |   | ٠ |   | • | • | blue-grey-red     |

| <i>ò</i> 4 - | R5                  |   | 10 ohms   | * |   |   |   |   | ٠ |   | brown-black-black |

| $i\Delta$    | R10, R11 (2 parts), | _ | 100 ohms  |   |   | ٠ |   | ٠ |   |   | brown-black-brown |

Figure 1

Install the ceramic disk and mylar capacitors. Without exception the value will be marked on the body of the part.

| DESI | GNATION           |            | VALUE               |

|------|-------------------|------------|---------------------|

| (4)  | C1-C4 (4 parts)   |            | 15 pf.              |

| (v)  | C5-C8 (4 parts)   |            | $.001 \mathrm{mfd}$ |

| (±/) | C9-C12 (4 parts)  |            | .1mfd. mylar        |

| (4)  | C13-C16 (4 parts) |            | .001 mfd.           |

| (v)  | C17-C20 (4 parts) | <b>.</b> 9 | 100pf.              |

| (≠)  | C21-C24 (4 parts) |            |                     |

Up to this point all components have been non-polarized and either lead could be placed in either of the holes provided without affecting the operation of the unit. Electrolytic capacitors are polarized and must be mounted so that the "+" lead of the capacitor goes through the "+" hole in the circuit board. In the event that the "-" lead of the capacitor is marked rather than the "+" lead it is to go through the unmarked hole in the circuit board.

Note that the operating voltage (v.) specified for a capacitor is the minimum acceptable rating. Capacitors supplied with specific kits may have a higher voltage rating than that specified and may be used despite this difference. For instance, a 100mfd. 25v. capacitor may be used in place of a 100mfd. 16v. capacitor without affecting the operation of the circuit.

Mount the following electrolytic capacitors and solder them in place. The values, voltage rating and polarization are marked on the body of the part.

| DESI              |     |   |   |  |  |  |   | VALUE               |      |

|-------------------|-----|---|---|--|--|--|---|---------------------|------|

| ( <sup>,/</sup> ) | C25 | • | ٠ |  |  |  | ٠ | $100\mathrm{mfd}$ . | 16v. |

|                   |     |   |   |  |  |  |   | 100mfd.             |      |

Install the integrated circuits. Note that a properly oriented integrated circuit will have a square notch or dimple at one end of the case that aligns with the semicircular designator printed on the circuit board. Use extreme care when installing integrated circuits. Like other semiconductors they are heat sensitive and should not be exposed to high temperatures for an extended period of time. Make sure that the integrated circuit is properly oriented before soldering it in place, as these units cannot be removed without destroying them,

NOTE: The integrated circuits used in this kit are MOS units that are sensitive to static electricity. When installing these units observe the following precautions: Do not wear synthetic materials such as nylon or rayon. Immediately before installing the IC's, touch a cold water pipe, or other source of good ground. Also touch the soldering iron tip to a grounded point. After all of the static electricity has been discharged, remove the IC from its holder, insert into the circuit board, and solder into place. Avoid excessive motion during this operation to keep static build-up to a minimum. Most manufacturers are installing static discharge paths in the IC itself, but we recommend these precautions for added safety.

In the following steps wires will be soldered to the circuit board which will in later steps connect to front panel controls and jacks. At each step prepare the wire by cutting it to the specified length and stripping 1/4" of insulation from each end of the wire. "Tin" each end by twisting the exposed strands tightly together and melting a small amount of solder into the wire.

Using the wire provided make the following connections to the circuit board,

```

a 4" length to point "A"

a 4 1/2" length to point "M0"

()

a 4" length to point "M1"

a 3 1/2" length to point "B"

()

()

a 2 1/2" length to point "C"

a 3 1/2" length to point "M2"

( )

( )

a 5 1/2" length to point "M3"

a 3" length to point "D"

( )

( )

a 5 1/2" length to point "E" "

a 4 1/2" length to point "VO"

( )

( )

a 5 1/2" length to point "F" "

a 2 1/2" length to point "V1"

( )

( )

a 6 1/2" length to point "G' "

a 3 1/2" length to point "V2"

()

( )

a 6 1/2" length to point "H' "

a 3 1/2" length to point "V3"

( )

```

The following wires will be installed as were those above except that  $1/2^n$  of insulation should be removed from the end of the wire which is not soldered to the circuit board.

```

( ) a 5 1/2" length to point "E" ( ) an 8" length to point "G" ( ) a 7" length to point "F" ( ) an 8 1/2" length to point "H"

```

THIS COMPLETES PRELIMINARY ASSEMBLY OF THE 8781 QUASH CIRCUIT BOARD

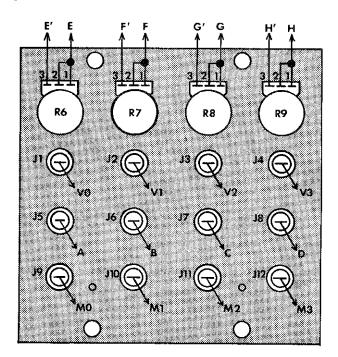

Temporarily lay the board aside and proceed to the mounting of the TINNERMAN NUT front panel controls and jacks. Place the front panel face down on a soft cloth to prevent marring the finish. (3 Place a red pin jack (J1) in the hole provided as shown in figure 3 and fasten in place with a Figure 2 tinnerman nut as shown in detail drawing figure 2. TINNERMAN NUT INSTALLATION

- In a similar manner, mount red pin jacks J2 J8 (7 parts) and fasten in place.

- (4) In a similar manner mount black pin jacks J9 J12 (4 parts) and fasten, in place.

Figure 3 FRONT PANEL PARTS PLACEMENT AND WIRING

- (/) Mount the 500K ohm potentiometer R6 in the location shown in figure 3. Use two 3/8" nuts, one behind the front panel as a spacer and the second on the front side of the front panel to secure the potentiometer. Adjust the rear nut so that none of the threaded shaft is exposed when the front nut is tightened down, this will allow the control knob, which will be mounted in a later step, to seat as closely as possible to the front panel. Orient as shown.

- ( /) In a similar manner, mount 500K pots R7 R9 (3 parts). Orient as illustrated.

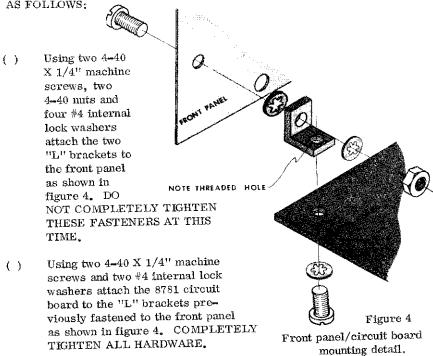

THE FRONT PANEL MAY NOW BE BOLTED TO THE CIRCUIT BOARD AS FOLLOWS:

REFERRING TO FIGURE 3 MAKE THE CONNECTIONS BETWEEN THE CIRCUIT BOARD AND FRONT PANEL AS FOLLOWS.

Route and dress all leads neatly as the connections are made.

| () F <sup>t</sup> lu | ; #3 R6<br>; #3 R7<br>1 assembly manual |

|----------------------|-----------------------------------------|

| ( | ) | G'               | ****************                       | lug #3 R8      |

|---|---|------------------|----------------------------------------|----------------|

| ( | ) | $\mathbf{H}^{+}$ | ****************                       | lub #3 R9      |

| ( | ) | $A_{\bullet}$    | ****************                       | J5             |

| ( | ) | В                |                                        | J6             |

| ( | ) | $\mathbf{C}$     |                                        | J7             |

| ( | ) | D                |                                        | J8             |

| ( | ) | M0               | ** * * * * * * * * * * * * * * * * * * | J9             |

| ( | ) | M1               | **********                             | J10            |

| ( | ) | M2               | ****************                       | J11            |

| ( | ) | M3               |                                        | $\mathbf{J}12$ |

NOTE that the following four wires connect to two lugs of the potentiometers involved.

| ( ) | E |                                        | lugs #1 & #2 R6 |

|-----|---|----------------------------------------|-----------------|

| ()  | F | ************************************** | lugs #1 & #2 R7 |

| ( ) | G |                                        | lugs #1 & #2 R8 |

| ( ) | H | *********                              | lugs #1 & #2 R9 |

( ) Install the 15 pin edge connector on the 8781 board as shown in detail in figure 5.

Figure 5

THIS COMPLETES ASSEMBLY OF THE 8781 QuASH.

#### SYSTEM WIRING

NOTE: The following is a highly recommended wiring schedule that should be followed exactly if you are going to be using your system with a PAIA 8700 Computer/Controller. If your system is to be used with other processors some changes to this schedule may be desirable and/or necessary.

From a system standpoint, the 8780 and 8781 should be considered to be a single unit, even though in the interest of versatility they are supplied separatel The 15 conductor cable supplied with the 8780 D/A will now be used to make connections between the 8780, 8781 and the 25 pin DB-25 connector which is supplied with the PAIA 8782 Encoded Keyboard.

( ) Locate the 15 conductor cable supplied with the PAIA 8780 Digital to Analog Converter and prepare it by removing 1-1/2" of the outer sheating from one end of the cable (we will now refer to this as the CONNECTOR END of the cable) and 4" from the other end (this is now the MODULE END of the cable).

Because of variations in suppliers of this cable it is not possible to predict the color coding of the wires in the cable. You should experience no problems if you fill in the blank space provided in the following wiring schedule with the color wire that you use for the specific connections listed.

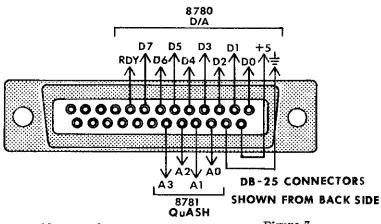

We will now use the 15 conductor cable partially prepared above to make connections between the 8780 D/A and the 25 pin DB-25 connector socket (female). NOTE: For neatest results, before making connections to the flea clips on the back of the D/A, cut each wire coming from the cable to a length only slightly longer than actually required. Strip 1/4" of insulation from the end of the wire being connected and tin the exposed wire strands. Simultaneou make the connections to the rear of the module and the DB-25 connector to decrease the likelihood of mistakes.

At the connector end also strip 1/4" of insulation from the wire and tin the exposed strands. It is also a good idea to pre-tin the pins of the DB-25 connector before connecting the wire. THESE CONNECTIONS ARE TIGHT... as you will soon discover. Take your time and be particularly careful of melting the insulation on the wires by overheating them.

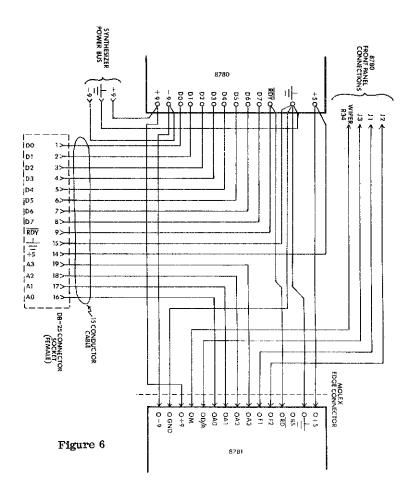

Following the procedures outlined above, make the following connections between the DB-25 connector and the 8780 D/A. (See figures 6 & 7.) NOTE that with the exception of the 4 address lines which will be added in the following steps, these connections are a sub-set of previously recommended wiring schedules (reference LAB NOTES - Computer Music Without the Computer; POLYPHONY 4/75 & I-COMP) If you have followed these schedules previously, removal and re-arrangement of this wiring is not necessary.

| 8780 DESIGNATION      | DB-25 Connector | Wire color                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cy Cu assault as male | pin #           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ( ) D0                | Ĵ.              | September 19 Marie Commission Commission (Commission of Commission of Co |

| ) Di                  | 2               | and the state of t |

| ( ) D2                | 3               | productive and the second seco |

| ( ) D3                | 4.              | we have the property of the state of the st  |

| () 104                | 5               | and the second section of the second  |

| () D5                 | 6               | An internal lines of the second of the secon |

| ( ) D6                | 7               | An and the first of the same o |

| ( ) D7                | 8               | Street a described by the second respectation and to the second respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ( ) RDŸ               | 9               | The second section of the section |

| ( ) +5                | 1.4             | man of the state o |

| ( )                   | 15              | The second description of the second descrip |

|                       |                 | . 3 /7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

The following are to be made between the DB-25 connector and the molex pin strip which mates with the Molex edge connector on the back of the 8781 QuASH card. At the male molex connector, the wires from the 15 conducto cable should be pre-tinned and wrapped around the shorter side of the pin before soldering. NOTE that there is no polarizing indication on the connector so care should be taken that the connector is not mistakenly switched end for end during assembly. Also keep in mind that systems which will be using multiple QuASH will require that second wires also be connected to the molex connector, leave from for them.

8781 assembly manual

Figure 7

| DB-25 Connector | 8781 EDGE   | Wire color  |

|-----------------|-------------|-------------|

| Pin #           | CONNECTOR   |             |

| () 16           | A0 (Pin 10) | <del></del> |

| () 17           | A1 (Pin 9)  | <del></del> |

| () 18           | A2 (Pin 8)  | Part        |

| () 19           | A3 (Pin 7)  | <del></del> |

There are several connections which must be made from flea clips on the rear edge of the 8780 D/A board to the 8781 edge connector. Note that several of the 8780 pins will ultimately have two wires connected to them and that one ( ) will eventually have 4. DO NOT rearrange this grounding scheme, one central ground point for modules in the 8780/8781 group is essential.

Make these connections using the indicated lengths of the insulated wire provided.

| 8780           | DESIGNATION   | 8781 EDGE<br>CONNECTOR           | WIRE<br>LENGTH |

|----------------|---------------|----------------------------------|----------------|

| ()             | +5 (2 wires)  | +5 (pin 1)                       | 6"t            |

| Ò              | = (2 wires)   | = (pin 2)                        | 611            |

| Ò              | RDY (2 wires) | $\overline{\mathrm{RD}}$ (pin 4) | 6**            |

| ò              | +9            | +9 (pin 13)                      | 611            |

| $\dot{\alpha}$ | -9            | -9 (pin 15)                      | 611            |

| $\dot{}$       | (3 wires)     | GND (pin 14)                     | 7 1/2          |

There are four connections which must be made from points on the FRONT PANEL of the 8780 D/A to pins on the edge connector of the 8781 QuASH. Make these connections using the indicated lengths of the insulated wire provided. These connections will be easier to make if the 8780 Front Panel is first removed.

| 8780 FRONT PANEL DESIGNATIONS ( ) J1 ( ) J2 | 8781 EDGE<br>CONNECTOR<br>F1 (pin 6)<br>F2 (pin 5) | WIRE<br>LENGTH<br>10 "<br>10 " |

|---------------------------------------------|----------------------------------------------------|--------------------------------|

| () J3                                       | D/A (pin 12)                                       | 11 ''                          |

| () Center Lug<br>(wiper) R34                | M (pin 11)                                         | 11 "                           |

While the 8780 D/A front panel is removed, it is a good idea to add a bypassing capacitor (.05 mfd., supplied) across this module's reference voltage input. Install this capacitor between the wiper of R34 and the grounding/mounting lug of the terminal strip which mounts C4 of the D/A. This capacitor bypasses digital noise which may otherwise be coupled into the reference input.

() Bypass capacitor ..... .05 mfd.

Reinstall the 8780 front panel and complete system wiring by preparing three 7 " lengths of insulated wire for use a power connections. These connections must be made from the flea clips on the 8780 D/A board to the power buss in the synthesizer system being used.

| 8780     |           | SYNTHESIZER |

|----------|-----------|-------------|

| DESIGNAT | ION       | POWER BUSS  |

| () +9    | (2 wires) | +9          |

| () -9    | (2 wires) | 9           |

| () 👆     | (4 wires) |             |

|          |           |             |

- ( ) Rotate the shafts of potentiometers R6-R9 fully counter-clockwise and press on four knobs so that the pointers are indicating 7:00 of an imaginary clock face.

- ( ) Make sure the \* jumper is installed to disable the 'bank select! line. Omit this jumper only if you are using software decoding+more than 4 QuASH.

THIS COMPLETES ASSEMBLY OF THE 8781 AND ITS INTERCONNECTIONS TO THE 8780. Carefully mate the Molex edge connector at the 8781 (be careful not to reverse it) and proceed to ADDRESS SELECTING and FINAL TEST.

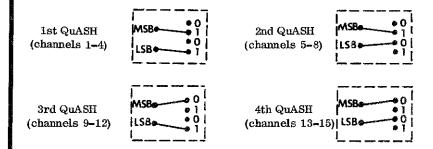

#### ADDRESS SELECTING 1

NOTE that the following assumes use of the QuASH in totally PAIA based systems and may need to be changed to be consistent with other processors/software. PAIA software assigns QuASH addresses in reverse numerical order, i.e. the first output channel of the system occupies address xxxF, the second xxxE, etc. The primary reason for this is to free the address xxxØ which in the PAIA system is reserved for selecting the D/A without selecting any accompanying sample and hold channel and for the cassette interface.

For PAIA standard systems, the address select jumpers on the 8781 should be set as follows:

Figure 8 Address Selecting

In systems using a single QuASH, the address select lines should be set up as in the "1st QuASH" configuration shown above.

#### TESTING AND FAMILIARIZATION

NOTE: The following procedures have been designed to minimize the amount and sophistication of the test equipment required but one piece of test equipment is essential – a computer. A module as software dependent as the QuASH can only be tested under computer control. The procedures are written assuming the use of a PAIA 8700 Computer/Controller but should be easily adaptable to other processors.

A second point - in order to eliminate the possibility of differences in oscillators being interpreted as problems in the 8781, the procedures are written using a <u>single VCO</u>. When the testing and familiarization procedures have been completed you will be ready to begin working with multiple oscillators and can then be fairly sure that any differences you may find in the control channels are differences in the oscillators.

Other test equipment required are a Volt-Ohm Meter and Voltage Controller Oscillator. If trouble shooting is required, an oscilloscope will be almost mandatory.

#### STATIC MODE TESTS

We will first put the QuASH through a series of "static mode" tests designed to verify the operation of the individual control channels. These tests will be implemented using the PIEBUG monitor to write control signals directly into the individual channels being tested.

Prepare for these and subsequent tests by connecting the 8780/8781 system to the DATA BUS connection of an operating 8700 Computer/Controller Apply power to the processor and connect the ±9v. power lines of the 8780/8781, provided during the preceding assembly instructions, to the synthesizer power bus or to an appropriate bench supply. After confirming that power has been properly applied to the entire system, press the 8700 RESET button and touch any control panel key. (1)

Using a VOM or DC coupled 'scope', confirm that the trigger outputs of all 4 QuASH control channels are cleared (0 volts). An alternate test to see that the flags are cleared would be to connect each trigger output in turn to the input of a 4740 or similar Envelope Generator (ADSR) and observe that the ADSR does not trigger.

Connect the control voltage output of the first S/H channel (A) to the input of an operating VCO (4720, 2720-2A, or equivalent) whose output you can monitor either through speakers or as a Lissajous pattern on a scope. (Various PAIA manuals outline Lissajous patterns, the 4720 and 2720-2A manuals are two.)

There will probably be <u>no output</u> at all from the oscillator since at this point we have not addressed any of the S/H channels and the normal output from a "dead" channel is zero volts.

If you do hear a tone, it may mean that during power up one or more of the channels was randomly addressed, but the tone should be gliding slowly down in pitch.

Write a  $\$00^{(2)}$  to the first control channel using the following keyboard entry sequence:

| STEP 1: | KEYSTROKES   | COMMENT                         |

|---------|--------------|---------------------------------|

|         | 0-9-F-F-DISP | ; sets pointer to the first S/H |

|         |              | ; channel, disregard display    |

|         | 0-0-ENT      | ; writes \$00 note to S/H       |

At this point you should hear (or see) a low pitched tone as the channel comes alive and the pitch of the tone should be adjustable over more than an octave range using the pitch control on the front panel of the 8780 D/A. The trigger flag on this channel should still be low.

Temporarily connect the oscillator to the control voltage outputs of the remaining 3 channels to verify that the control voltage is appearing only at the channel we just addressed.

Next, we will write a \$3F (corresponding to the highest control voltage) into the S/H channel as follows:

| STEP 2: | KEYSTROKES | COMMENT                                 |

|---------|------------|-----------------------------------------|

|         | BACK       | ; the monitor automatically incremented |

|         |            | ; to location 0A00-we now go back to    |

|         |            | ; 09FF. Keystroke de-selects channel    |

|         |            | ; so pitch will decay.                  |

|         | 3-F-ENT.   | ; write high pitch to S/H channel       |

and the oscillator should quickly step to a high pitch (64 semi-tones higher than the first) and should still be adjustable using the  $\rm D/A$  pitch control. Temporarily connect the VCO to the three remaining outputs to once again make sure that only the addressed channel is responding.

Test to make sure that the trigger flag is working by writing the previous note in to the S/H channel with the trigger flag set (\$7F):

| STEP 3: | KEYSTROKE    | COMMENT                                 |

|---------|--------------|-----------------------------------------|

|         | BACK-7-F-ENT | ; pitch decay will still be present     |

|         |              | ; when channel de-selected, but because |

|         |              | ; of high pitch less noticeable.        |

<sup>(2)</sup> The dollar sign (\$) is an almost universal indication that the number which follows it is in Hexidecimal.

and test the trigger output to see that it is now set. Also check the trigger flags on the remaining channels and confirm that they are cleared.

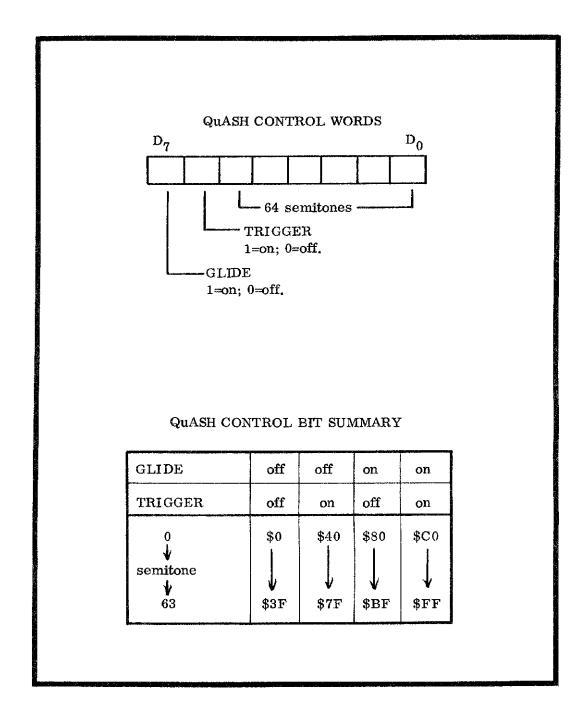

You may now make a very rough check of the glide circuit's operation by turning the glide control of the channel being tested fully clockwise and writing to the channel the lowest pitched note only now with the glide control bit set:

STEP 4: KEYSTROKE COMMENT

BACK-8-0-ENT; \$80-lowest pitch, trigger cleared,

; glide turned on,

Observe that there is an easily discernible slew downscale rather than an instantaneous step. DO NOT be concerned that the glide seems fast, it will be much faster during this static test than it will be during normal dynamic operation.

Successful completion of these tests indicates that the first S/H channel is operating normally. REPEAT THIS SERIES OF TESTS FOR THE REMAINING 3 S/H CHANNELS.

In testing these remaining channels, only the keyboard entries at step 1 will change (steps 2-4 will be identical) and these entries should be:

For Channel B:

0~9-F-E-DISP-0-0-ENT.

For Channel C:

0-9-F-D-DISP-0-0-ENT.

For Channel D:

0~9-F-C-DISP-0-0-ENT.

In each case, these entries set the PIEBUG pointer to the address of the S/H channel to be tested and writes the first entry (\$00) to that channel.

Successful completion of the static mode tests outlined are a strong indication that the 8781 has been properly assembled and that the wiring between it and the 8780 is correct. We now need to check the operation of the unit in its dynamic mode, under program control:

Here is a quick and dirty dynamic test program that we can use:

| ADDRESS       | LABEL  | CODE     | INSTRUCTION    | COMMENTS                              |

|---------------|--------|----------|----------------|---------------------------------------|

| 0000          | TEST   | A9 10    | LDA #10        | ; set up note                         |

| 02            | REPEAT | A2 10    | LDX #10        | ; set up S/H pointer                  |

| 04            | LOOP1  | 9D EF 09 | STA S/H, x     | ; update S/H                          |

| 07            |        | 8E 20 08 | STX DISP       | ; show in display <b>–</b><br>working |

| 0A            |        | A0 10    | LDY #10        | ; set up delay                        |

| 0C            | LOOP2  | 88       | DEY            | ; delay                               |

| 0D            |        | D0 FD    | BNE LOOP2      |                                       |

| $\mathbf{0F}$ |        | CA       | $\mathbf{DEX}$ | ; point to next S/H                   |

| 10            |        | D0 F2    | BNE LOOP1      | ; if not done, loop                   |

| 12            |        | F0 EE    | BEQ REPEAT     | ; branch always<br>repeat             |

This program actually updates and maintains 16 channels of S/H so that it can be used for up to 4 QuASH.

Load the program from the 8700 keyboard and after stepping back through it to double check that it has been entered correctly, run it by entering the starting address (0000) followed by the RUN key. Turn the pitch control of the 8780 D/A fully clockwise.

As this program runs it writes the same note (#10) into all S/Hs. With the program running, connect the input of your test oscillator to each of the control voltage channels in sequence and see that they are all producing the same voltage – as indicated by the oscillator producing the same pitch for all channels. Any differences in the channels can almost certainly be traced to off-sets in the S/H amplifiers. If you notice objectionable differences, contact PAIA.

The note that is written to the control channels by the above program is first loaded to the accumulator by the LoaD Accumulator immediate instruction and its companion operand at memory locations \$0000 and \$0001. If you want to alter the program to write different notes or notes with various control function enabled you should do it by changing the operand for this instruction. Tables of notes and control functions and the data required to produce them are included in the "summary" section at the end of this manual.

For example, if you wish to change the program so that it generates the same note as it does currently, only with glide selected and trigger set you would change memory location 0001 from its current value of \$10 to \$D0:

| KEY SEQUENCE       | DISPLAY SHOWS               |

|--------------------|-----------------------------|

| RESET-0-0-0-1-DISP | 10; the data currently in   |

|                    | ; location 0001             |

| D-0                | Do; the new data.           |

| ENTER              | A2: the instruction at 0002 |

Note that this program will not reveal any problems caused by "crossed" control channels (you address one channel but actually write to another). Detection of these sorts of problems is the function of the static mode tests.

SUCCESSFUL COMPLETION OF THESE STATIC AND DYNAMIC MODE TESTS ARE A STRONG INDICATION THAT YOUR 8781 IS FUNCTIONING NORMALLY

USING THE 8781 - Hardware level

It is important to think of the 8781 as just another control voltage and trigger source, much the same as a keyboard.

It is also very important to realize that the 8781 has very little character of its own. Its personality is defined almost exclusively by the soft-ware which supports it.

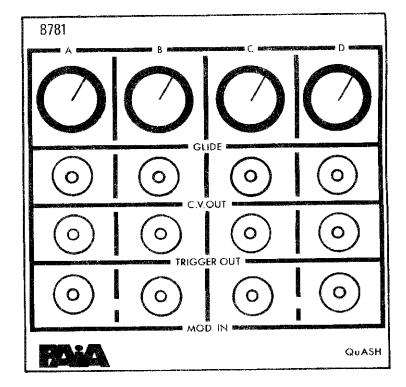

But with or without software, the front panel controls and jacks of the 8781 are designed to perform specific functions as follows:

NOTE that the QuASH front panel is divided into 4 separate sections, one for each of the "control channes!" A, B, C and D. Inputs and Outputs to each channel are arranged in verticle columns.

GLIDE - The topmost control in each channel column is the GLIDE rate control. Clockwise rotation of this control increases the time required to glide from one control voltage to the next. Glide must be selected digitally for this control to be operational, allowing computer selection and deselection of a glide rate set by the front panel controls.

C.V. OUT - This red pin jack directly below the GLIDE control is the control voltage output of the channel. Depending on the software being used, this may be either pitch information for Voltage Controlled Oscillators, transient waveforms (as with software ADSRs) of other analog control signals.

TRIGGER OUT - The middle red pin jack in each column is a binary triggering signal which with most software will indicate that there is a key down corresponding to the analog pitch voltage appearing at the C.V. output jacks. In most cases this corresponds to a normal synthesizer's "gate" signal and will be used to initiate hardware ADSR or other transient generator action.

MOD IN - This black pin jack at the bottom of each column provides a means of adding modulation control voltages to the channel; as, for example, adding vibrato by applying a sine wave. This is a DC coupled input which has its own offset (less than O.S.V.) from ground which must be taken into account when adding control voltages.

It is a chromatic input; a voltage which transposes by a semi-tone in low octaves will also transpose by a semi-tone at high octaves.

It is a non-interactive input. Modulation voltage applied to these inputs will affect the control voltage output of only that channel and will not interact with control voltages either from other outputs of the same QuASH or others in the system.

#### SOME USEFUL TIPS

When using the QuASH, keep the pitch control of the D/A in the system set as high as practical to minimize offset errors in the Sample/Hold amplifiers.

On control voltage changes corresponding to several octaves you may notice that the output does not transition from the initial control voltage to the final one in a single step, but rather transitions in a very rapid succession of steps. This should not be objectionable in most cases as it will be masked by attack dynamics. In cases where it is objectionable it can be overcome with software, but at the expense of maximum glide rate.

Long glides (on the order of seconds) should be handled with software.

#### USING THE 8781 - software level

QuASH are designed to be most easily used in memory mapped output architectures in which each QuASH channel occupies a single address location within a specified contiguous block of addresses.

The enabling line or lines of the D/A being used to provide control voltage signals to the QuASH (RDY on the 8780) must be arranged to respond to any address within the range of addresses occupied by QuASH. The "Simplified QuASH Address Map" in the summary section of this manual lists QuASH addresses as they map onto the PAIA 8700 Computer/Controller.

Since for minimum error some settling time of the D/A should be provided before a corresponding QuASH is addressed, there should be at least one address in the map which is occupied solely by the D/A (in the current configuration of the 8700, address \$0900 is used, but it is not the only address that meets this criterion).

Typical program flow would be to write the desired output data first to the address occupied only by the D/A, followed by writing the same data to the desired control channel address:

| LDA NOTES, x | ; get output data from NOTES<br>; table output buffer location<br>; specified by pointer x |

|--------------|--------------------------------------------------------------------------------------------|

| STA D/A      | ; write data to D/A - and ; settle                                                         |

| STA S/H,×    | ; write settled control voltage<br>; to control channel specified<br>; by pointer x        |

It is also desirable to allow a longer delay for the S/H to stabilize, the program steps above would ordinarily be followed by something like this:

| DELAY | LDY#04          | ; set up a counter for the ; delay                   |

|-------|-----------------|------------------------------------------------------|

| LOOP  | DEY<br>BNE LOOP | ; decrement delay counter<br>; loop 'til delay done. |

An interesting aspect of this S/H delay is that it is a control of the duty factor of the analog control voltage applied to the S/H channels and the observant reader will rightfully imply that offers the potential for limited software control of glide rate.

The Polytonic synthesizer program listing provided in the addenda to this manual should illustrate a number of useful concepts in programming fo the PAIA 8700 standard system.

#### **SUMMARY**

SIMPLIFIED QuASH ADDRESS MAP BASE ADDRESS 0900

| QuASH# |                        | CHA | NNEL                     |      |                           |

|--------|------------------------|-----|--------------------------|------|---------------------------|

|        | A                      | В   | С                        | D    |                           |

| 1      | $\mathbf{F}\mathbf{F}$ | FE  | FD                       | FC   |                           |

| 2      | FB                     | FA  | $\mathbf{F9}$            | F8   |                           |

| 3      | F7                     | F6  | F5                       | F4   | * In systems using mor    |

| 4      | $\mathbf{F}3$          | F2  | $\mathbf{F1}$            | F0*  | than 15 channels, each 8  |

| 5      | $\mathrm{EF}^{*}$      | EE* | $\mathbf{E}\mathbf{D}^*$ | EC*  | BS pin must be tied to ad |

| 6      | EB*                    | EA* | E9*                      | E8*  | ress line 5 (A4 - J7 pin  |

| 7      | $\mathbf{E7}^{*}$      | E6* | E5*                      | E4*  | ON ALL 8781 MODULES       |

| 8      | E3*                    | E2* | E1*                      | E 0* | THE SYSTEM.               |

To determine the address of a specific S/H channel, add the address of the channel as shown above to the base address 0900, eg. the address of channel B of the first QuASH is 09FE.

#### DATA (in HEX) AND CORRESPONDING NOTE NAMES

|                   | OCTAVE |    |     |    |    |    |

|-------------------|--------|----|-----|----|----|----|

| NOTE              | 0      | 1  | 2   | 3  | 4  | 5  |

| $G^{\#}$          | 00     | 0C | 18  | 24 | 30 | 3C |

| A                 | 01     | 0D | 19  | 25 | 31 | 3D |

| $A^{\#}$          | 02     | 0E | 1A  | 26 | 82 | 3E |

| В                 | 03     | 0F | 1B  | 27 | 33 | 3F |

| C                 | 04     | 10 | 1C  | 28 | 34 | *  |

| C#                | 05     | 11 | 1D  | 29 | 35 |    |

| D                 | 06     | 12 | 1E  | 2A | 36 |    |

| $\mathbf{D}^{\#}$ | 07     | 13 | 1.F | 2B | 37 |    |

| E                 | 08     | 14 | 20  | 2C | 38 |    |

| F                 | 09     | 15 | 21  | 2D | 39 |    |

| $\mathrm{F}^{\#}$ | 0A     | 16 | 22  | 2E | 3A |    |

| G                 | 0B     | 17 | 23  | 2F | 3B |    |

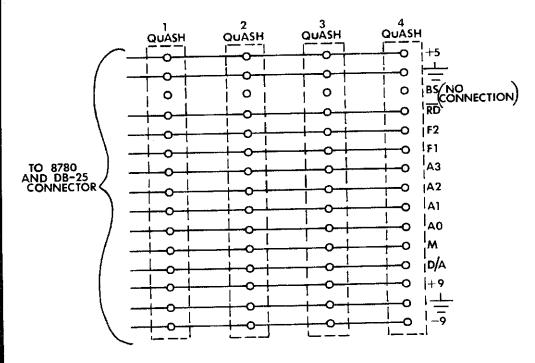

Shaded area represents PAIA 8782 Keyboard active area. NOTE: Moving across horizontal rows transposes by octaves. Up to 4 QuASH (16 output channels) may be bussed together in a single system simply by connecting the pins of the connectors together in a one-to-one correspondence as shown in figure 9.

Figure 9 QuASH Bussing

Expansion beyond 16 outputs requires that external address decoding be supplied to the Bank Select (BS) enabling inputs of the QuASH units. Otherwise, no connections need be made to these points.

## NOTES